### United States Patent [19]

#### Carter et al.

#### [54] MULTIPLE B-ADJACENT GROUP ERROR CORRECTION AND DETECTION CODES AND SELF-CHECKING TRANSLATORS THEREFOR

- [75] Inventors: William C. Carter, Ridgefield, Conn.; Edward P. Hsieh, Yorktown Heights; Aspi B. Wadia, Chappaqua, both of N.Y.

- [73] Assignce: International Business Machines Corporation, Armonk, N.Y.

- [22] Filed: Sept. 26, 1972

- [21] Appl. No.: 247,071

- [52] U.S. Cl. ...... 340/146.1 AL, 235/153 AM

- [51] Int. Cl. ..... H04l 1/10, G11c 29/00

#### [56] **References Cited**

UNITED STATES PATENTS

3,697,949 10/1972 Carter et al. ...... 340/146.1 AL

#### OTHER PUBLICATIONS

Patel, A. M., Error Correcting Code for Hybrid Errors, In IBM Tech. Disc. Bull. 14(4): p. 1288–1290, Sept. 1971.

Primary Examiner—Eugene G. Botz Assistant Examiner—R. Stephen Dildine, Jr. Attorney—Isidore Match et al.

# [45] Oct. 16, 1973

[11]

3,766,521

#### [57] ABSTRACT

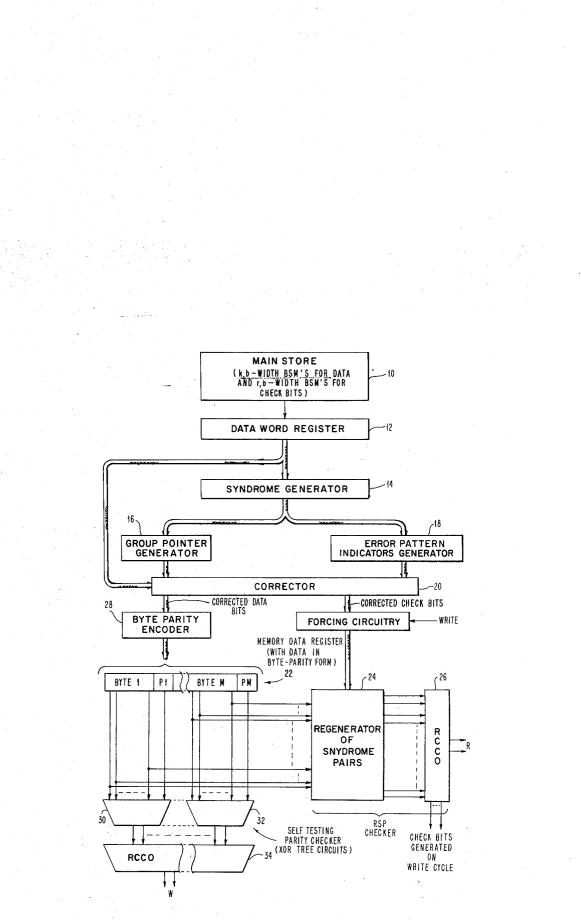

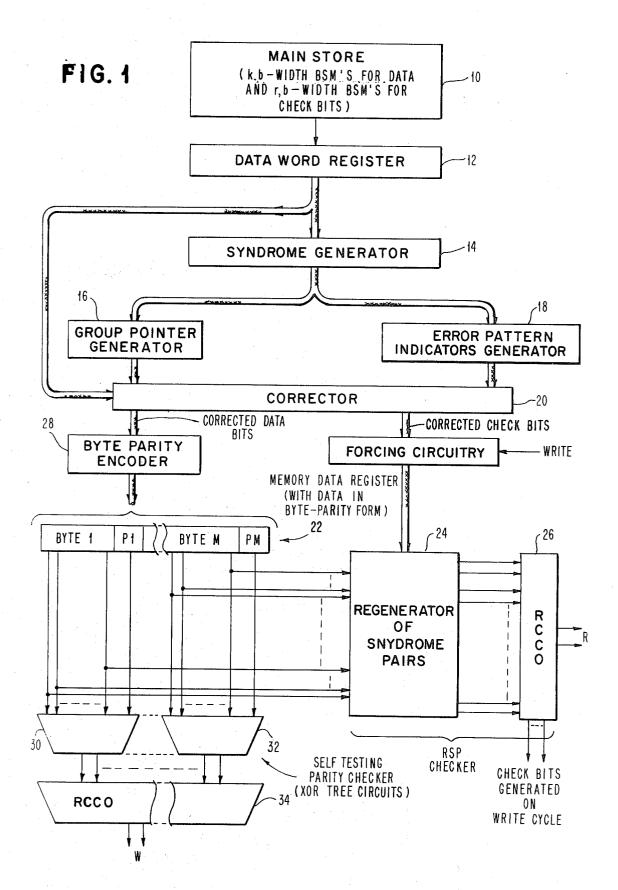

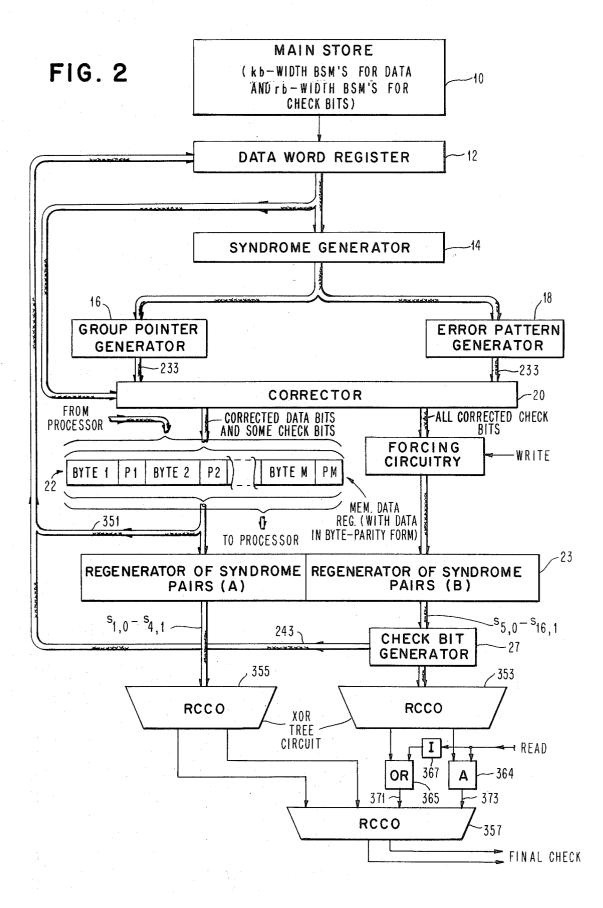

Novel error correction and detection codes and selfchecking translators therefor are disclosed. A first of these codes is a t b-adjacent bit group error correcting d-adjacent bit group error detecting code using a quantity of 2t+d groups of b check bits. This code with a b-bit BSM (basic storage module) memory organization is capable of correcting b-adjacent errors due to failures in any t basic storage modules, detecting badjacent errors due to failures in any t+d basic storage modules, and, because of the translator design, detecting with high probability b-adjacent errors in 2t+2d-1storage modules where  $1 \le t$ ,  $0 \le d$ . If k b-bit BSM's are needed for data, then t and d may be chosen as any integers such that  $k+2t+d \leq 2^{b}+1$ , and  $2t+d \leq 2^{b}$ -1. In this case k+2+d b-bit BSM's are needed for coded word storage. Correction of b-adjacent errors means that if errors occur in from 1 to b bits in any pattern in the output of a b-bit BSM, these bit errors will be corrected. Self-checking translators are provided for these codes which employ substantially less circuitry than known translators for the same purpose. The failure-tolerance capabilities of these translators are such that every single failure in the translator circuitry is either detected or does not cause erroneous output and the probable accumulation of undetected failures in the translator circuitry before ultimate detection does not produce any erroneous output that goes undetected.

#### 28 Claims, 45 Drawing Figures

# United States Patent [19]

Carter et al.

# 3,766,521

SHEET 01 OF 39

3,766,521

SHEET 02 OF 39

3,766,521

8

#### SHEET 030F 39

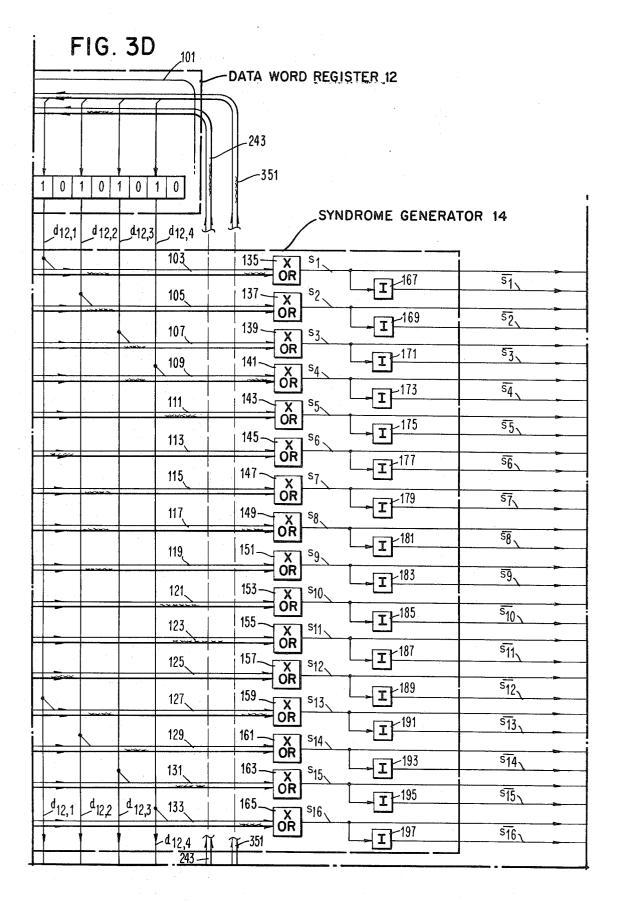

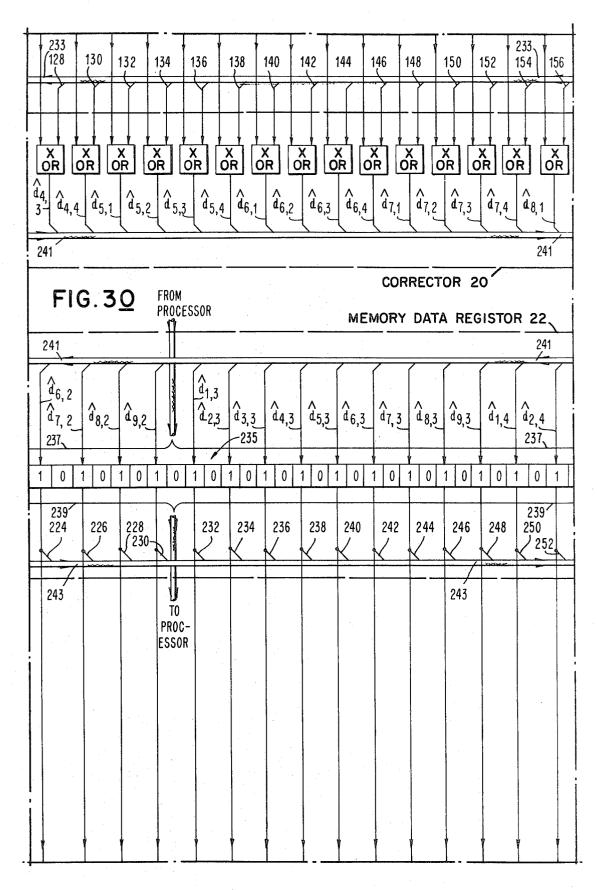

DATA WORD REGISTER 12

|           |          | <b>U</b> . |         |                    |        | 01                                     | AIA V  | VORD              | REGI     | STER  | 12~                |        |                   |              |

|-----------|----------|------------|---------|--------------------|--------|----------------------------------------|--------|-------------------|----------|-------|--------------------|--------|-------------------|--------------|

|           | 101.     | 43         |         |                    |        | ************************************** |        |                   |          |       |                    |        | 01                | 243          |

|           | -196     | -214       | -232    | -250               | -198   | -216                                   | -234   | -252              | -200     | -218  | -236               | -254   | -202              | 220          |

|           |          |            | 10      | 1 0                | 10     | 10                                     | 1 0    |                   | 10       | 10    | 1 0                | 10     | 10                | 1 0          |

|           | _d1,1    | _a1,2      | _d1,3   | L <sup>a</sup> 1,4 | d 2, 1 | d2,2                                   | _d 2,3 | d2,4              | d.3,1    | _d3,2 | · · · · · ·        | d3,4   | _d4,1             | d 4,2        |

|           |          |            |         |                    |        |                                        |        |                   |          |       | 103 <u></u><br>105 |        |                   |              |

|           |          |            |         |                    |        |                                        |        |                   | - HORNEY |       | 107                |        |                   |              |

|           |          |            |         |                    |        |                                        |        |                   |          |       | 109                |        |                   |              |

|           |          |            | <br>    |                    |        |                                        |        |                   |          |       | 111                |        |                   |              |

|           |          |            | <b></b> |                    |        |                                        |        |                   |          |       | 113                |        |                   | -            |

| 칙         | <b>^</b> |            |         |                    |        |                                        |        |                   |          |       | 115                |        |                   | -            |

| VTOR      |          |            |         |                    |        |                                        |        |                   |          |       | 117                |        |                   | <u></u>      |

| GENERATOR |          |            |         |                    |        |                                        |        |                   |          |       | 119<br>121         |        | -                 |              |

| ROME GI   |          |            |         |                    |        |                                        |        | <u>}</u>          |          |       | 123                |        |                   |              |

| SYNDRO    |          |            |         |                    |        |                                        |        |                   |          |       | 125                |        | <u> </u>          |              |

|           |          |            |         | <u> </u>           |        |                                        |        |                   |          |       | 127                |        | <u>`</u>          |              |

| •         |          |            |         |                    |        | (                                      |        |                   |          |       | 129                |        |                   |              |

|           | da       |            |         |                    |        |                                        |        |                   |          |       | 131                |        | <u> </u>          |              |

|           | d1, 1    | 1,2        | _d1,3   | _ <u>_</u> @1,4    | d2,1   | -ª2,2                                  | -d2,3  | -d <sub>2,4</sub> | -d3,1    | -d3,2 | $\rightarrow$      | _d3, 4 | -d <sub>4,1</sub> | <u>d</u> 4,2 |

|           |          |            |         |                    | ·      |                                        |        |                   |          |       | 133                |        |                   |              |

# 3,766,521

# SHEET 04 OF 39

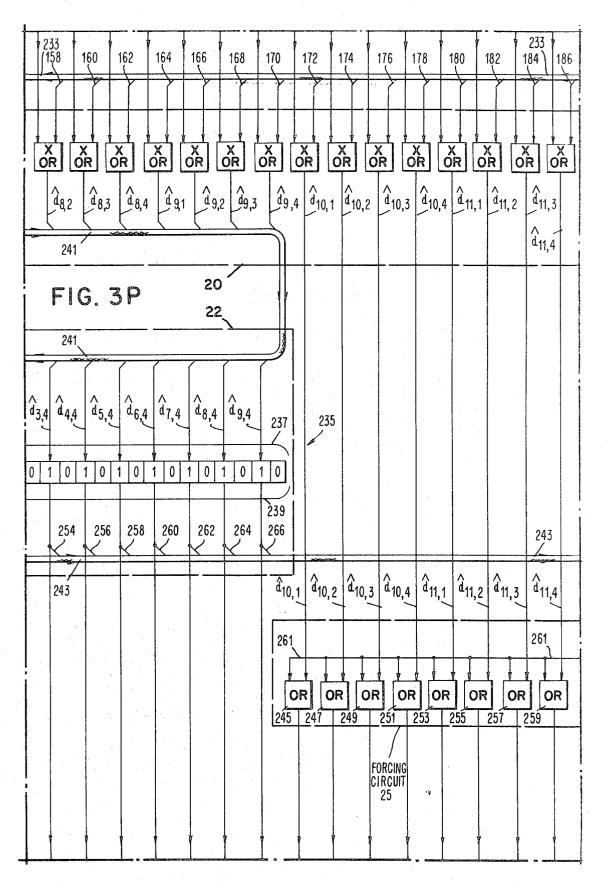

| 101 2            |                   |                  |                  |       |                  |                  | _                |                                 |                  |                |          |          |                  |                  |

|------------------|-------------------|------------------|------------------|-------|------------------|------------------|------------------|---------------------------------|------------------|----------------|----------|----------|------------------|------------------|

| 238              | _ <u>~ ~</u><br>[ |                  |                  |       |                  |                  |                  | ••                              |                  |                |          | 24       | 3_10             | 1                |

|                  | -256              | -204             | -222             | -240  | -258             | -206             | -224             | -242                            | -260             | -208           | -226     | -244     | -262             | 210              |

|                  | 0 1               | 0 1              |                  | 0     | 1 0 1            | 0                |                  |                                 |                  | ۴<br>۱   0   1 | ¥<br>0 1 | 0 1      |                  | 1 0              |

| d <sub>4,3</sub> | d 4,4             | <sup>d</sup> 5,1 | <sup>d</sup> 5,2 | d 5,3 | <sup>d</sup> 5,4 | <sup>d</sup> 6,1 | d <sub>6,2</sub> | d <sub>6,3</sub><br>1 <u>14</u> | d <sub>6,4</sub> | d7,1           | d7,2     | d 7, 3   | <sup>d</sup> 7,4 | <sup>d</sup> 8,1 |

|                  |                   |                  |                  |       |                  | 103<br>105       |                  |                                 |                  |                |          |          |                  |                  |

|                  |                   |                  |                  |       |                  | 107              | and the second   |                                 |                  |                |          |          |                  |                  |

|                  | <u> </u>          |                  |                  |       |                  | 109              |                  |                                 |                  | 20000          |          |          |                  |                  |

|                  | -<br>             | incor            |                  |       |                  | 111<br>113       |                  | -                               |                  |                |          | <u> </u> |                  | 1                |

|                  | <u> </u>          |                  |                  |       |                  | 115              |                  |                                 |                  | <u> </u>       |          |          |                  |                  |

|                  | <u> </u>          | MACINE           |                  |       |                  | 117              |                  |                                 |                  |                |          |          |                  |                  |

|                  |                   |                  |                  |       |                  | 119              |                  |                                 |                  |                |          |          | wise the         |                  |

|                  |                   |                  |                  |       |                  | 121              |                  |                                 |                  |                |          |          |                  | -                |

|                  |                   |                  |                  |       |                  | 125              |                  |                                 |                  |                |          |          |                  |                  |

|                  |                   |                  |                  |       |                  | 127              |                  |                                 |                  |                |          |          |                  |                  |

|                  |                   |                  |                  |       |                  | 129              |                  |                                 |                  |                |          |          |                  |                  |

| d                | d <sub>4,4</sub>  | -d 5 4           | dra              | _d5 z | _d5,4            | 131<br>          | _d6 2            | _d <sub>6,3</sub>               | d6 4             | _d71           | ¢72      | d73      | _d7.4            | d.8.1            |

| -"4,3            | -4,4              | -0,1             | -0,2             | -J,J  |                  | 133              | V 0,2            | 14                              |                  | Y              | P ', C   |          |                  |                  |

3,766,521

# SHEET 05 OF 39

| FIG. 3C                             | TO AND I    | ROM MAIN           | STORE I      | BSM'S 1             | 0                   |                    |                      | 10,1                | <1 <sup>1</sup> | 2                  | 3,51                   |

|-------------------------------------|-------------|--------------------|--------------|---------------------|---------------------|--------------------|----------------------|---------------------|-----------------|--------------------|------------------------|

| 243                                 | .101        | ۶.                 |              |                     |                     |                    | ,                    |                     |                 | _/                 | +<br>                  |

| 228 246 264                         | -212 -230   | 248                | -266         |                     |                     |                    |                      |                     |                 | 243                | <del>f</del> =         |

|                                     |             | 10                 | 10           | 1 0 ·               | 1 0                 | 1 0                | 10                   | ¥<br>1 0            | ♥<br>1 0        | 10                 | 1<br>0                 |

| <u>d8,2</u> <u>d8,3</u> <u>d8,4</u> | d9,1 d9,    | 2 <sup>d</sup> 9,3 |              | _ <sup>d</sup> 10,1 | d 10,2              | d10,3              | <sup>d</sup> 10,4    | <sup>d</sup> 11,1   |                 | d-11,3             | d <sub>11,</sub><br>14 |

|                                     |             |                    | 103<br>105   |                     |                     |                    |                      |                     | 1 <u>14</u>     | 4 24430            | -                      |

|                                     |             |                    | 107          |                     |                     |                    |                      |                     |                 |                    |                        |

|                                     |             |                    | 109<br>111   | <br>                |                     |                    |                      |                     |                 |                    |                        |

|                                     |             |                    | 113          |                     |                     |                    |                      |                     |                 |                    |                        |

|                                     |             | -                  | 115          |                     |                     |                    |                      |                     |                 |                    |                        |

|                                     |             |                    | 117          |                     |                     |                    | <u> </u>             |                     |                 |                    |                        |

|                                     |             |                    | 119          |                     |                     |                    |                      |                     |                 |                    |                        |

|                                     |             |                    | 121<br>123   |                     |                     |                    |                      |                     |                 |                    | -                      |

|                                     |             |                    | 125          |                     |                     |                    |                      |                     |                 |                    |                        |

|                                     |             | _                  | 127          |                     |                     |                    | -                    |                     |                 |                    |                        |

|                                     |             |                    | 129          |                     | ->                  |                    |                      |                     |                 |                    |                        |

| d8,2 d8,3 d8,4                      | _d9,1 _d9,1 | 2                  | 131<br>d 9,4 | _d 10, 1            | _ <sup>d</sup> 10,2 | _d <sub>10,3</sub> | _ <sup>d</sup> 10, 4 | _ <sup>d</sup> 11,1 | d11, 2          | <sup>d</sup> 11, 3 | d <sub>11,4</sub>      |

|                                     |             |                    | 133          |                     |                     |                    |                      |                     | <u>14</u>       | 1                  |                        |

3.766,521

#### SHEET 06 OF 39

3.766,521

SHEET 07 OF 39

.

3,766,521

SHEET 08 OF 39

3,766,521

SHEET 09 OF 39

3.766,521

SHEET 10 OF 39

# 3.766,521

# SHEET 11 OF 39

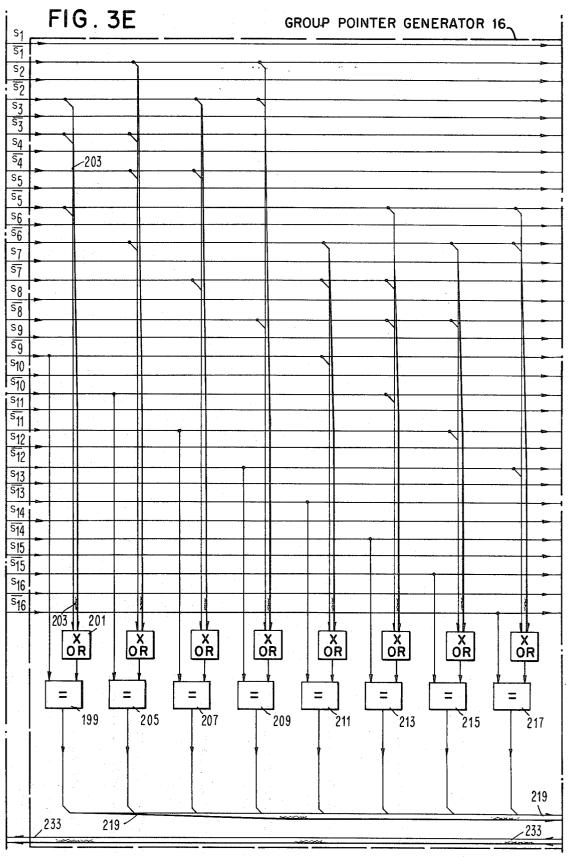

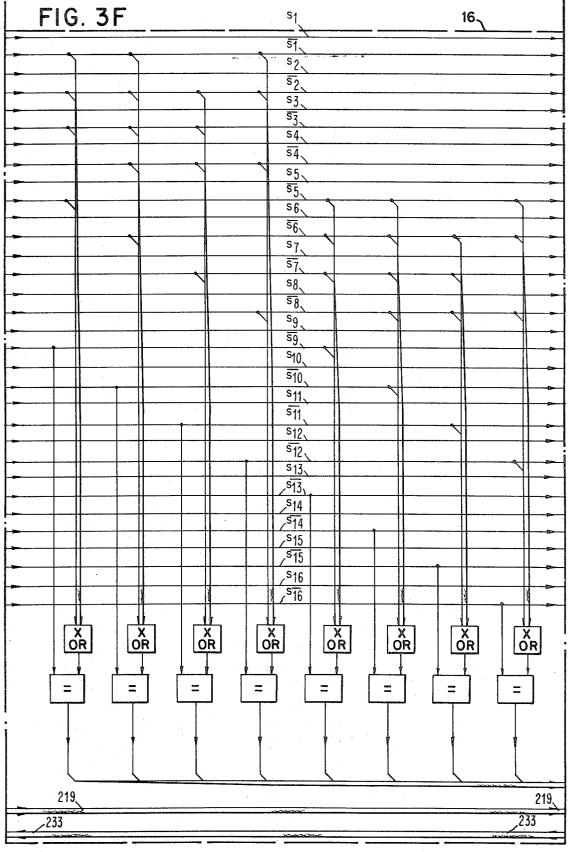

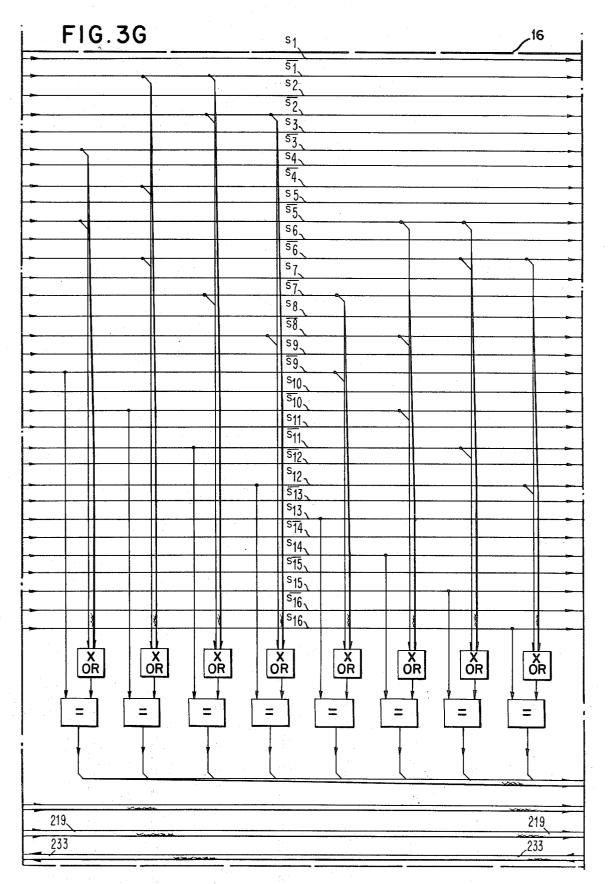

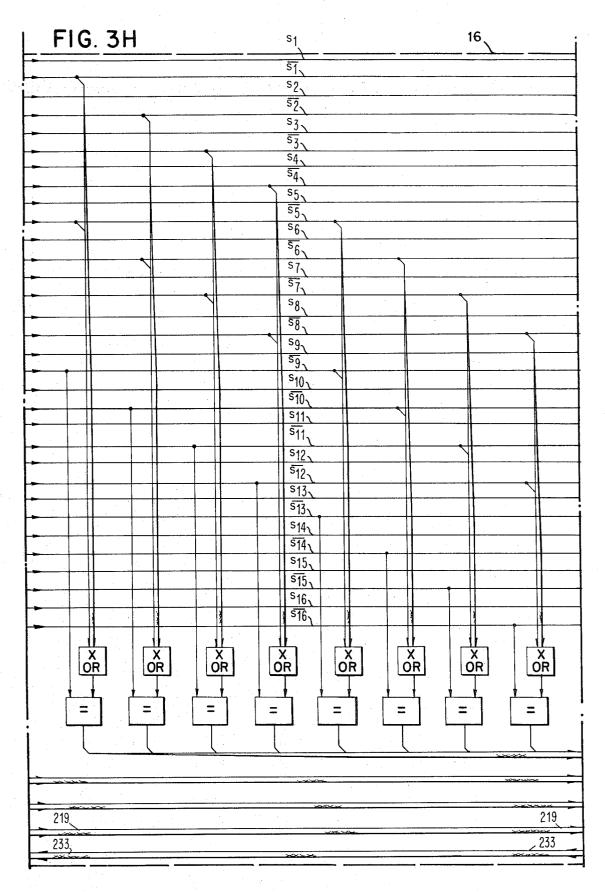

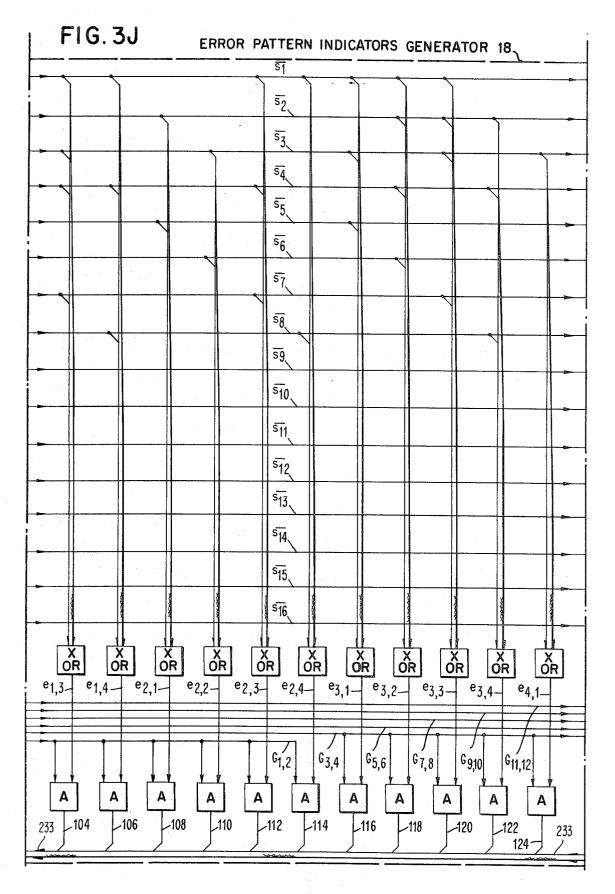

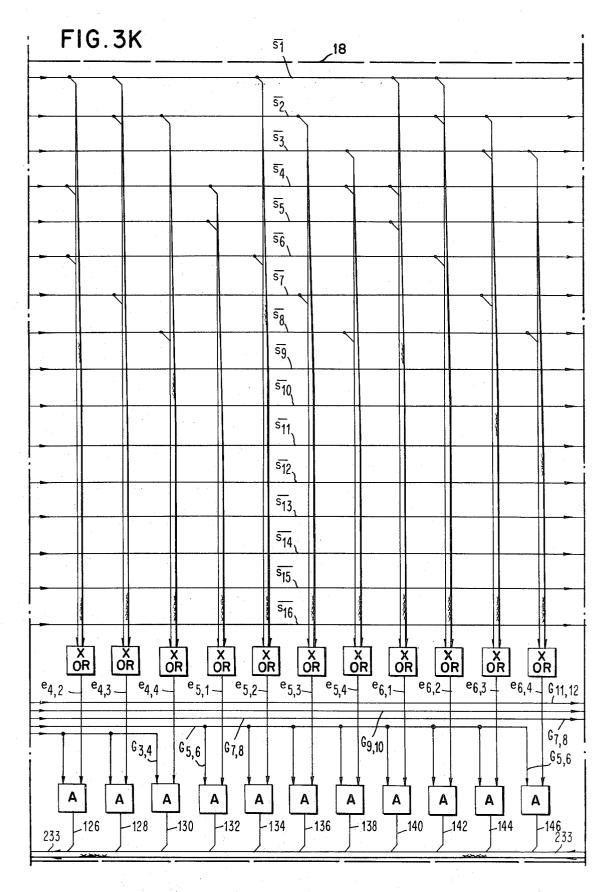

| FIG. 31GROUP POINTER GENERATOR 16                                                                                                                           | ERROR PATTERN   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|                                                                                                                                                             |                 |

| s <sub>2</sub>                                                                                                                                              |                 |

| s3                                                                                                                                                          | 53              |

| s <sub>4</sub>                                                                                                                                              | <u> </u>        |

| s <sub>5</sub>                                                                                                                                              | 55              |

| s                                                                                                                                                           | 56,             |

| s <sub>7</sub>                                                                                                                                              | <u> </u>        |

|                                                                                                                                                             | S8              |

| sg                                                                                                                                                          | sg s            |

| \$10                                                                                                                                                        | 5 <u>10</u>     |

|                                                                                                                                                             | s <sub>11</sub> |

|                                                                                                                                                             | 5 <u>12</u>     |

|                                                                                                                                                             | 513             |

|                                                                                                                                                             | 5 <u>1</u> 4    |

|                                                                                                                                                             | <u> </u>        |

|                                                                                                                                                             |                 |

|                                                                                                                                                             |                 |

| G 11, 12                                                                                                                                                    |                 |

| 231 A 69,10                                                                                                                                                 |                 |

| 229 A 67,8<br>227 A 65,6                                                                                                                                    |                 |

| $\begin{array}{c} 225 \\ \hline \\ 219 \\ \hline \\ 219 \\ \hline \\ 223 \\ \hline \\ \\ 223 \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ |                 |

| 233 221                                                                                                                                                     |                 |

3.766,521

#### SHEET 120F 39

# 3.766,521

#### SHEET 130F 39

#### SHEET 14 OF 39

3,766,521

### SHEET 15 OF 39

3,766,521

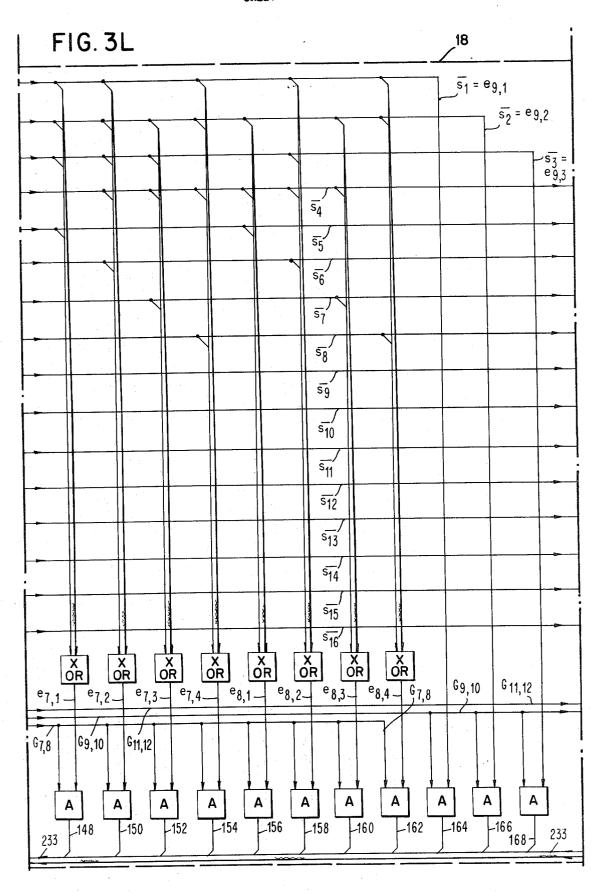

SHEET 16 0F 39

3,766,521

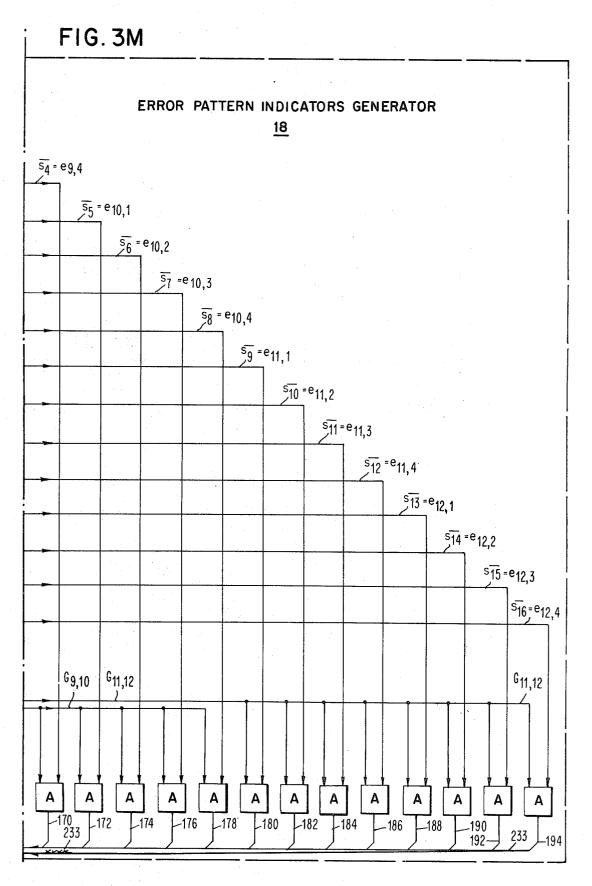

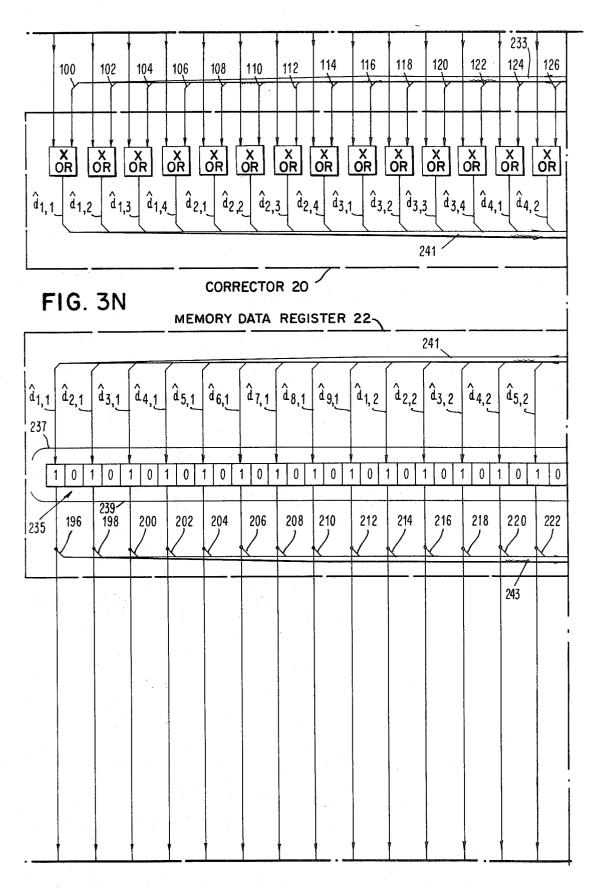

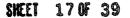

### 3.766,521

#### SKEET 1805 39

3.766,521

SHEET 190F 39

# 3,766,521

#### SHEET 200F 39

# 3.766,521

SHEET 210F 39

# 3,766,521

# SHEET 22 OF 39

# 3.766,521

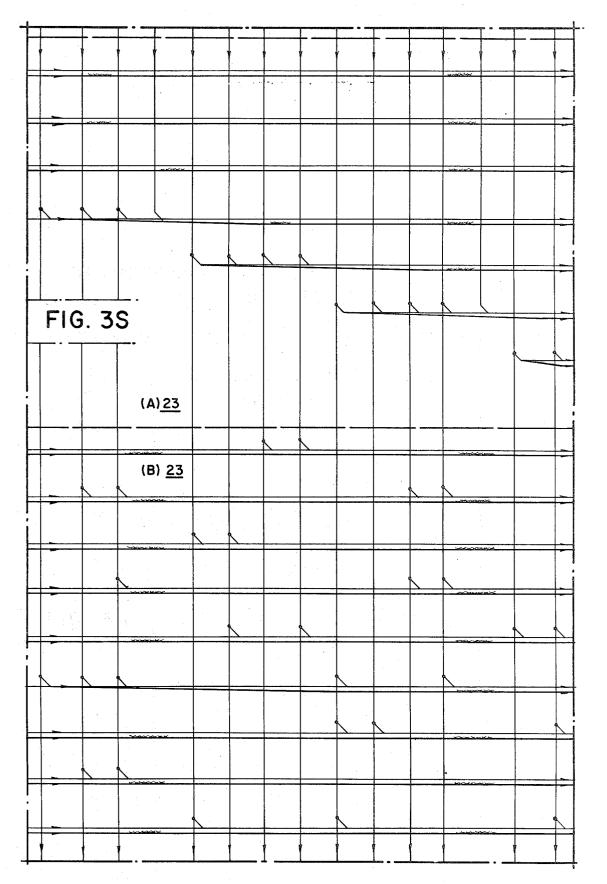

#### SHEET 230F 39

÷

3,766,521

# 3.766,521

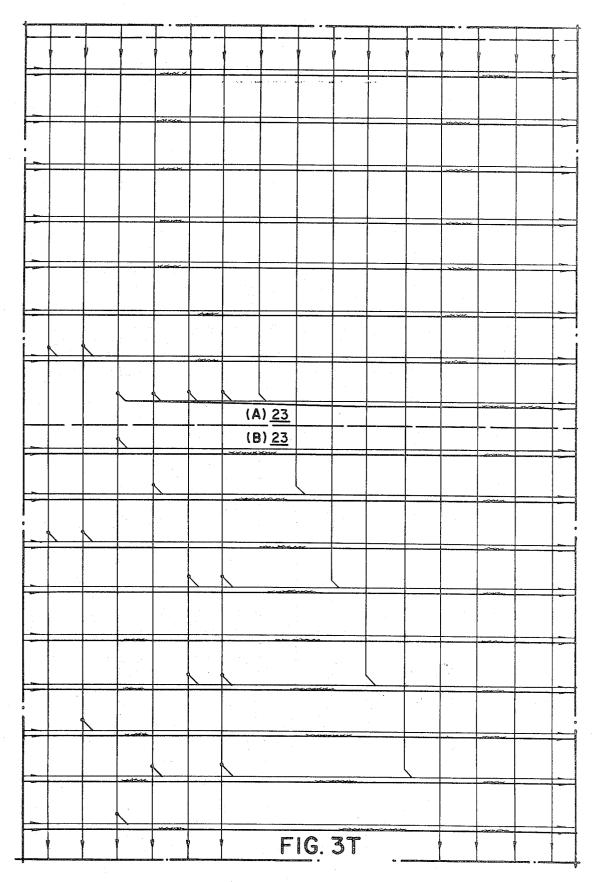

SHEET 25 0F 39

23

# 3.766,521

SHEET 26 OF 39

# 3.766,521

# SHEET 27 OF 39

# 3.766,521

SHEET 28 OF 39

3,766,521

3.766,521

### SHEET 30 OF 39

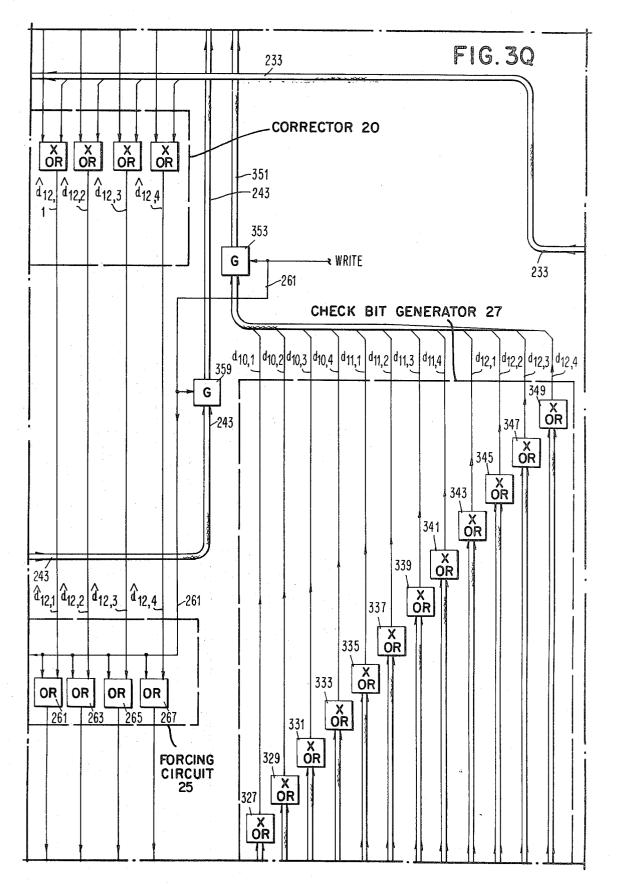

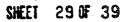

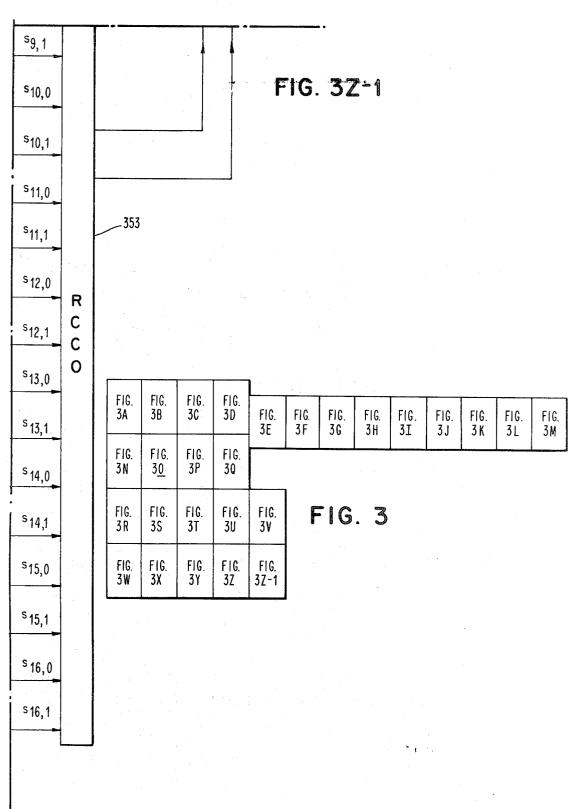

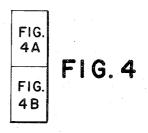

# FIG. 4A

# EQUATIONS PERTAINING TO SYNDROME GENERATOR

DATA WORD =  $d_{1,1}, d_{1,2}, d_{1,3}, d_{1,4}, \dots, d_{12,1}, d_{12,2}, d_{12,3}, d_{12,4}$

| $\begin{bmatrix} s_{1} \\ s_{2} \\ s_{3} \\ s_{4} \end{bmatrix} = \begin{bmatrix} s_{5} \\ s_{6} \\ s_{7} \\ s_{8} \end{bmatrix} = \begin{bmatrix} s_{9} \\ s_{10} \\ s_{11} \\ s_{12} \end{bmatrix} = \begin{bmatrix} s_{13} \\ s_{14} \\ s_{15} \\ s_{16} \end{bmatrix}$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $s_i = d_{1,i} \oplus d_{2,i} \oplus \cdots \oplus d_{12,i}$ FOR $i = 1, 2, 3, 4$                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                            |

| $s_5 = d_{1,2} \oplus d_{2,1} \oplus d_{2,2} \oplus d_{3,3} \oplus d_{4,1} \oplus d_{4,3} \oplus d_{5,1} \oplus d_{5,4} \oplus d_{6,4} \oplus d_{7,2} \oplus d_{7,3} \oplus d_{8,1}$                                                                                       |

| $\oplus d_{8,2} \oplus d_{8,3} \oplus d_{10,1}$                                                                                                                                                                                                                            |

| $s_6 = d_{1,3} \oplus d_{2,2} \oplus d_{2,3} \oplus d_{3,1} \oplus d_{3,4} \oplus d_{4,1} \oplus d_{4,2} \oplus d_{4,4} \oplus d_{5,1} \oplus d_{5,2} \oplus d_{6,1}$                                                                                                      |

| $\oplus d_{7,1} \oplus d_{7,3} \oplus d_{7,4} \oplus d_{8,1} \oplus d_{8,2} \oplus d_{8,3} \oplus d_{8,4} \oplus d_{10,2}$                                                                                                                                                 |

|                                                                                                                                                                                                                                                                            |

| $s_7 = d_{1,1} \oplus d_{1,4} \oplus d_{2,1} \oplus d_{2,3} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,2} \oplus d_{4,1} \oplus d_{4,2} \oplus d_{4,3} \oplus d_{5,2}$                                                                                                      |

| $\oplus d_{5,3} \oplus d_{6,2} \oplus d_{7,2} \oplus d_{7,4} \oplus d_{8,2} \oplus d_{8,3} \oplus d_{8,4} \oplus d_{10,3}$                                                                                                                                                 |

|                                                                                                                                                                                                                                                                            |

| $s_8 = d_{1,1} \oplus d_{2,1} \oplus d_{2,4} \oplus d_{3,2} \oplus d_{4,2} \oplus d_{4,4} \oplus d_{5,3} \oplus d_{6,3} \oplus d_{6,4} \oplus d_{7,1} \oplus d_{7,2}$                                                                                                      |

| $\oplus d_{8,1} \oplus d_{8,2} \oplus d_{8,4} \oplus d_{10,4}$                                                                                                                                                                                                             |

3.766,521

# SKEET 31 OF 39

$$s_{9} = d_{1,3} \oplus d_{2,1} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,2} \oplus d_{4,2} \oplus d_{5,1} \oplus d_{5,3} \oplus d_{5,4} \oplus d_{6,3} \oplus d_{6,4} \\ \oplus d_{7,1} \oplus d_{7,2} \oplus d_{7,3} \oplus d_{8,2} \oplus d_{8,3} \oplus d_{11,1} \\ s_{10} = d_{1,1} \oplus d_{1,4} \oplus d_{2,1} \oplus d_{2,2} \oplus d_{2,4} \oplus d_{3,2} \oplus d_{3,3} \oplus d_{4,3} \oplus d_{5,2} \oplus d_{5,4} \oplus d_{6,4} \\ \oplus d_{7,1} \oplus d_{7,2} \oplus d_{7,3} \oplus d_{7,4} \oplus d_{8,1} \oplus d_{8,3} \oplus d_{8,4} \oplus d_{11,2} \\ s_{11} = d_{1,1} \oplus d_{1,2} \oplus d_{2,1} \oplus d_{2,2} \oplus d_{2,3} \oplus d_{3,1} \oplus d_{3,3} \oplus d_{3,4} \oplus d_{4,1} \oplus d_{4,4} \oplus d_{5,1} \\ \oplus d_{5,3} \oplus d_{6,1} \oplus d_{7,1} \oplus d_{7,2} \oplus d_{7,4} \oplus d_{8,2} \oplus d_{8,4} \oplus d_{11,3} \\ s_{12} = d_{1,2} \oplus d_{2,2} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,4} \oplus d_{4,1} \oplus d_{5,2} \oplus d_{5,3} \oplus d_{6,2} \oplus d_{6,3} \oplus d_{6,4} \\ \oplus d_{7,1} \oplus d_{7,2} \oplus d_{7,4} \oplus d_{8,4} \oplus d_{1,4} \\ s_{13} = d_{1,1} \oplus d_{1,2} \oplus d_{2,2} \oplus d_{2,3} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,3} \oplus d_{3,4} \oplus d_{4,1} \oplus d_{4,2} \oplus d_{4,4} \\ \oplus d_{7,1} \oplus d_{7,2} \oplus d_{7,4} \oplus d_{8,2} \oplus d_{1,1} \\ s_{13} = d_{1,1} \oplus d_{1,2} \oplus d_{2,3} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,3} \oplus d_{3,4} \oplus d_{4,1} \oplus d_{4,2} \oplus d_{4,3} \\ \oplus d_{5,1} \oplus d_{5,2} \oplus d_{5,4} \oplus d_{6,2} \oplus d_{6,3} \oplus d_{6,4} \oplus d_{7,1} \oplus d_{8,1} \oplus d_{12,1} \\ \\ s_{14} = d_{1,1} \oplus d_{1,2} \oplus d_{2,3} \oplus d_{2,4} \oplus d_{3,2} \oplus d_{12,2} \\ \\ s_{15} = d_{1,2} \oplus d_{1,3} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,3} \oplus d_{4,1} \oplus d_{4,2} \oplus d_{4,3} \oplus d_{5,1} \oplus d_{5,2} \\ \oplus d_{5,3} \oplus d_{6,3} \oplus d_{6,4} \oplus d_{7,2} \oplus d_{8,2} \oplus d_{12,2} \\ \\ s_{15} = d_{1,2} \oplus d_{1,3} \oplus d_{2,4} \oplus d_{3,1} \oplus d_{3,3} \oplus d_{4,1} \oplus d_{4,2} \oplus d_{4,3} \oplus d_{4,4} \oplus d_{5,1} \\ \oplus d_{5,2} \oplus d_{5,3} \oplus d_{5,4} \oplus d_{6,4} \oplus d_{7,3} \oplus d_{8,3} \oplus d_{12,3} \\ \\ s_{16} = d_{1,3} \oplus d_{2,1} \oplus d_{2,2} \oplus d_{2,3} \oplus d_{2,4} \oplus d_{3,2} \oplus d_{3,3} \oplus d_{12,3} \\ \\ s_{16} = d_{1,3} \oplus d_{2,1} \oplus d_{2,2} \oplus d_{2,3} \oplus d_{2,4} \oplus d_{3,2} \oplus d_{3,3} \oplus d_{12,4} \\ \\ \oplus d_{5,3} \oplus d_{6,1} \oplus d_{6,2} \oplus d_{6,3} \oplus d_{6,4} \oplus d_{7,4} \oplus d_{8,4} \oplus d_{12,4} \\ \\ \oplus d_{5,3} \oplus d_{6,1} \oplus d_{6,2} \oplus d_{6,3} \oplus d_{6,4} \oplus d_{7,4} \oplus d_{8,4} \oplus d_{12,4} \\ \\ \oplus d_{5,3} \oplus d_{6,1} \oplus d_{6,2} \oplus d_{6,3} \oplus d_{6,4} \oplus d_{7,4} \oplus d_{8,4} \oplus d_{12,4} \\ \\ \oplus d_{5,3} \oplus d_{6,1} \oplus d_{6,2} \oplus d_{6,3} \oplus d_$$

FIG. 4B

3,766,521

#### SHEET 32 OF 39

# FIG. 5

### EQUATIONS PERTAINING TO GROUP POINTER GENERATOR

| $\mathfrak{G}_{1,2} = \left[\overline{\mathfrak{s}_9} = \left(\overline{\mathfrak{s}_5} \oplus \overline{\mathfrak{s}_2} \oplus \overline{\mathfrak{s}_3}\right)\right] \wedge \left[\overline{\mathfrak{s}_{10}} = \left(\overline{\mathfrak{s}_6} \oplus \overline{\mathfrak{s}_1} \oplus \overline{\mathfrak{s}_3} \oplus \overline{\mathfrak{s}_4}\right)\right]$                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\wedge \left[\overline{s_{11}} = \left(\overline{s_7} \oplus \overline{s_2} \oplus \overline{s_4}\right)\right] \wedge \left[\overline{s_{12}} = \left(\overline{s_8} \oplus \overline{s_1} \oplus \overline{s_2}\right)\right]$                                                                                                                                                                                                       |

| $\wedge \left[\overline{s_{13}} = \left(\overline{s_9} \oplus \overline{s_6} \oplus \overline{s_7}\right)\right] \wedge \left[\overline{s_{14}} = \left(\overline{s_{10}} \oplus \overline{s_5} \oplus \overline{s_7} \oplus \overline{s_8}\right)\right]$                                                                                                                                                                              |

| $\wedge \left[ \begin{array}{c} \overline{s_{15}} = \left( \overline{s_{11}} \oplus \overline{s_6} \oplus \overline{s_8} \right) \right] \wedge \left[ \overline{s_{16}} = \left( \overline{s_{12}} \oplus \overline{s_5} \oplus \overline{s_6} \right) \right]$                                                                                                                                                                        |

| $\mathfrak{G}_{3,4} = \left[\overline{\mathfrak{s}_9} = \left(\overline{\mathfrak{s}_5} \oplus \overline{\mathfrak{s}_1} \oplus \overline{\mathfrak{s}_2} \oplus \overline{\mathfrak{s}_3}\right)\right] \wedge \left[\overline{\mathfrak{s}_{10}} = \left(\overline{\mathfrak{s}_6} \oplus \overline{\mathfrak{s}_1} \oplus \overline{\mathfrak{s}_2} \oplus \overline{\mathfrak{s}_3} \oplus \overline{\mathfrak{s}_4}\right)\right]$ |

| $\wedge \left[\overline{s_{11}} = (\overline{s_7} \oplus \overline{s_2} \oplus \overline{s_3} \oplus \overline{s_4})\right] \wedge \left[\overline{s_{12}} = (\overline{s_8} \oplus \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_4})\right]$                                                                                                                                                                                 |

| $\wedge \left[\overline{s_{13}} = \left(\overline{s_9} \oplus \overline{s_5} \oplus \overline{s_6} \oplus \overline{s_7}\right)\right] \wedge \left[\overline{s_{14}} = \left(\overline{s_{10}} \oplus \overline{s_5} \oplus \overline{s_6} \oplus \overline{s_7} \oplus \overline{s_8}\right)\right]$                                                                                                                                  |

| $\wedge \left[ \overline{s_{15}} = \left( \overline{s_{11}} \oplus \overline{s_6} \oplus \overline{s_7} \oplus \overline{s_8} \right) \right] \wedge \left[ \overline{s_{16}} = \left( \overline{s_{12}} \oplus \overline{s_5} \oplus \overline{s_6} \oplus \overline{s_8} \right) \right]$                                                                                                                                             |

| ${}^{G}5, \mathfrak{g} = \left[\overline{s_9} = \left(\overline{s_5} \oplus \overline{s_3}\right)\right] \wedge \left[\overline{s_{10}} = \left(\overline{s_6} \oplus \overline{s_1} \oplus \overline{s_4}\right)\right] \wedge \left[\overline{s_{11}} = \left(\overline{s_7} \oplus \overline{s_1} \oplus \overline{s_2}\right)\right]$                                                                                               |

| $\wedge \left[\overline{s_{12}} = (\overline{s_8} \oplus \overline{s_2})\right] \wedge \left[\overline{s_{13}} = (\overline{s_9} \oplus \overline{s_7})\right] \wedge \left[\overline{s_{14}} = (\overline{s_{10}} \oplus \overline{s_5} \oplus \overline{s_8})\right]$                                                                                                                                                                 |

| $\wedge \left[\overline{s_{15}} = \left(\overline{s_{11}} \oplus \overline{s_5} \oplus \overline{s_6}\right)\right] \wedge \left[\overline{s_{16}} = \left(\overline{s_{12}} \oplus \overline{s_6}\right)\right]$                                                                                                                                                                                                                       |

| $G_{7,8} = \left[\overline{s_9} = \left(\overline{s_5} \oplus \overline{s_1}\right)\right] \wedge \left[\overline{s_{10}} = \left(\overline{s_6} \oplus \overline{s_2}\right)\right] \wedge \left[\overline{s_{11}} = \left(\overline{s_7} \oplus \overline{s_3}\right)\right]$                                                                                                                                                         |

| $\wedge \left[\bar{s_{12}} = (\bar{s_8} \oplus \bar{s_4})\right] \wedge \left[\bar{s_{13}} = (\bar{s_9} \oplus \bar{s_5})\right] \wedge \left[\bar{s_{14}} = (\bar{s_{10}} \oplus \bar{s_6})\right]$                                                                                                                                                                                                                                    |

| $\wedge \left[\overline{s_{15}} = (\overline{s_{11}} \oplus \overline{s_7})\right] \wedge \left[\overline{s_{16}} = (\overline{s_{12}} \oplus \overline{s_8})\right]$                                                                                                                                                                                                                                                                   |

| 16 - 2                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $G_{9,10} = \bigwedge_{i=8}^{16} (\overline{s_i} = 0) = s_8 \wedge s_9 \wedge s_{10} \dots \wedge s_{16}$                                                                                                                                                                                                                                                                                                                               |

| $G_{11,12} = \bigwedge_{i=1}^{8} \left( \overline{s_i} = 0 \right) = S_1 \wedge S_2 \wedge S_3 \dots \wedge S_8$                                                                                                                                                                                                                                                                                                                        |

# 3,766,521

# SHEET 330F 39

# FIG.6A

#### EQUATIONS PERTAINING TO ERROR PATTERN GENERATOR

| FIG.6      |                                                  |                                                                                                                      |

|------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| FIG.<br>6A | $e_{1,1} = \overline{s_1} \oplus \overline{s_2}$ | $\oplus \overline{s}_5$                                                                                              |

| FIG.       | $e_{1,2} = \overline{s_2} \oplus \overline{s_3}$ | ⊕ <del>5</del> 6                                                                                                     |

| 6B         | $e_{1,3} = \overline{s_1} \oplus \overline{s_3}$ | $\oplus \overline{s_4} \oplus \overline{s_7}$                                                                        |

|            | $e_{1,4} = \overline{s_1} \oplus \overline{s_4}$ | $\oplus \overline{\mathfrak{s}_{\vartheta}}$                                                                         |

|            | $e_{2,1} = \overline{s_2} \oplus \overline{s_5}$ |                                                                                                                      |

|            | $e_{2,2} = \overline{s_3} \oplus \overline{s_6}$ |                                                                                                                      |

|            | $e_{2,3} = \overline{s_1} \oplus \overline{s_4}$ | ⊕ \$7                                                                                                                |

|            | $e_{2,4} = \overline{s_1} \oplus \overline{s_8}$ |                                                                                                                      |

|            | $e_{3,1} = \overline{s_1} \oplus \overline{s_3}$ | $\oplus \overline{s_5}$                                                                                              |

|            | $e_{3,2} = \overline{s_1} \oplus \overline{s_2}$ | $\oplus \overline{s_4} \oplus \overline{s_6}$                                                                        |

|            | $e_{3,3} = \overline{s_1} \oplus \overline{s_2}$ | $\oplus \overline{s_3} \oplus \overline{s_7}$                                                                        |

|            | $e_{3,4} = \overline{s_2} \oplus \overline{s_4}$ | $\oplus \overline{s_{\vartheta}}$                                                                                    |

|            | $e_{4,1} = \overline{s_3} \oplus \overline{s_5}$ |                                                                                                                      |

|            | $e_{4,2} = \overline{s_1} \oplus \overline{s_4}$ | $\oplus \overline{s_6}$                                                                                              |

|            | $e 4, 3 = \overline{s_1} \oplus \overline{s_2}$  | ⊕ <sup>5</sup> 7                                                                                                     |

|            | $e_{4,4} = \overline{s_2} \oplus \overline{s_8}$ | ана на селото на село<br>Х |

|            | $e_{5,1} = \overline{s_4} \oplus \overline{s_5}$ |                                                                                                                      |

|            | $e_{5,2} = \overline{s_1} \oplus \overline{s_6}$ |                                                                                                                      |

|            | $e_{5,3} = \overline{s_2} \oplus \overline{s_7}$ |                                                                                                                      |

| •          | I                                                |                                                                                                                      |

3.766,521

SHEET 34 OF 39

| • •                                                  |                                                                                                                    | -                                                                                                               |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                                      | $e_{5,4} = \overline{s_3} \oplus \overline{s_4} \oplus \overline{s_8}$                                             |                                                                                                                 |

|                                                      | $e_{6,1} = \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_5}$                                             |                                                                                                                 |

|                                                      | $e_{6,2} = \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_6}$                                             |                                                                                                                 |

|                                                      | $e_{6,3} = \overline{s_2} \oplus \overline{s_3} \oplus \overline{s_7}$                                             | -                                                                                                               |

|                                                      | $e_{6,4} = \overline{s_3} \oplus \overline{s_8}$                                                                   |                                                                                                                 |

|                                                      | $e_{7,1} = \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_3} \oplus \overline{s_5}$                       |                                                                                                                 |

|                                                      | $e_{7,2} = \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_3} \oplus \overline{s_4} \oplus \overline{s_6}$ |                                                                                                                 |

|                                                      | $e_{7,3} = \overline{s_2} \oplus \overline{s_3} \oplus \overline{s_4} \oplus \overline{s_7}$                       |                                                                                                                 |

|                                                      | $e_{7,4} = \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_4} \oplus \overline{s_8}$                       |                                                                                                                 |

| FIG.6B                                               | $e_{8,1} = \overline{s_2} \oplus \overline{s_4} \oplus \overline{s_5}$                                             |                                                                                                                 |

|                                                      | $e_{8,2} = \overline{s_1} \oplus \overline{s_3} \oplus \overline{s_4} \oplus \overline{s_6}$                       |                                                                                                                 |

|                                                      | $e_{8,3} = \overline{s_2} \oplus \overline{s_4} \oplus \overline{s_7}$                                             |                                                                                                                 |

|                                                      | $e_{8,4} = \overline{s_1} \oplus \overline{s_2} \oplus \overline{s_8}$                                             |                                                                                                                 |

|                                                      | $e_{9,1} = \overline{s_1}$ $e_{11,1} = \overline{s_9}$                                                             |                                                                                                                 |

|                                                      | $e_{9,2} = \overline{s_2}$ $e_{11,2} = \overline{s_{10}}$                                                          | And the second state of the second |

| ter di secondo<br>Secondo Secondo<br>Secondo Secondo | $e_{9,3} = \overline{s_3}$<br>$e_{11,3} = \overline{s_{11}}$                                                       |                                                                                                                 |

|                                                      | $e_{9,4} = \overline{s_4}$ $e_{11,4} = \overline{s_{12}}$                                                          |                                                                                                                 |

|                                                      | $e_{10,1} = \overline{s_5}$ $e_{12,1} = \overline{s_{13}}$                                                         |                                                                                                                 |

|                                                      | $e_{10,2} = \overline{s_6}$ $e_{12,2} = \overline{s_{14}}$                                                         |                                                                                                                 |

|                                                      | $e_{10,3} = \overline{s_7}$ $e_{12,3} = \overline{s_{15}}$                                                         |                                                                                                                 |

|                                                      | $e_{10,4} = \overline{s_8}$<br>$e_{12,4} = \overline{s_{16}}$                                                      |                                                                                                                 |

| . <b>.</b>                                           |                                                                                                                    |                                                                                                                 |

### PATENTED OCT 16 1973

3.766,521

### SHEET 35 OF 39

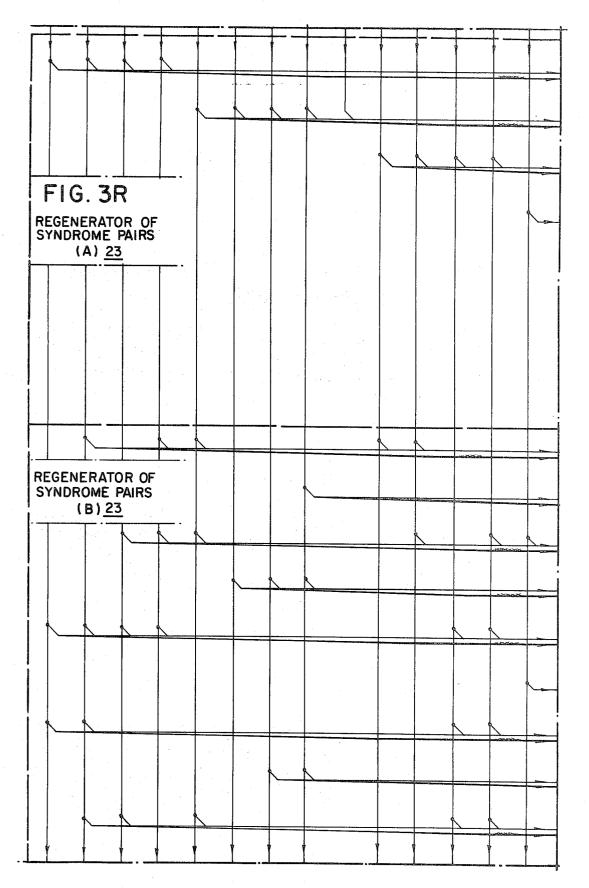

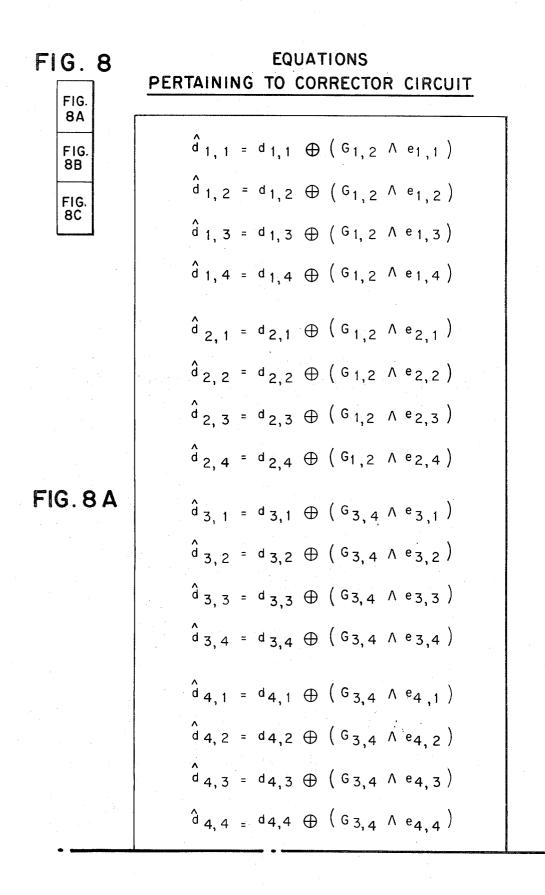

# FIG. 7A

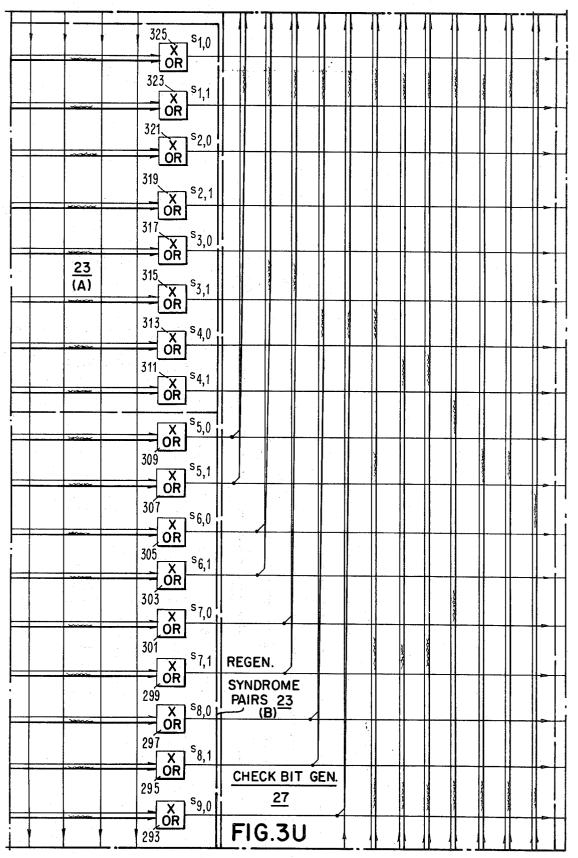

### EQUATIONS PERTAINING TO REGENERATION OF SYNDROME PAIRS

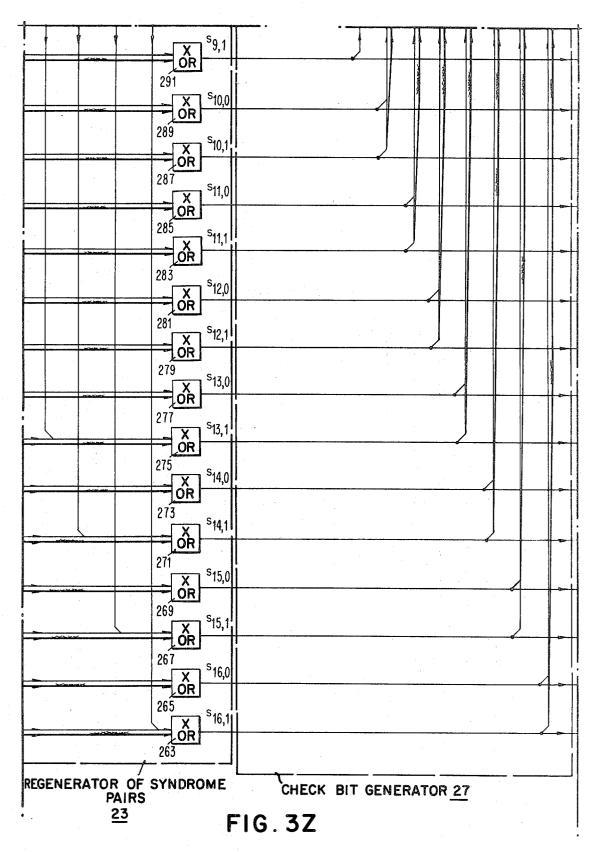

$s_{5,0} = \hat{d}_{1,2} \oplus \hat{d}_{2,1} \oplus \hat{d}_{2,2} \oplus \hat{d}_{3,3} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,3} \oplus \hat{d}_{5,1} \oplus \hat{d}_{5,4}$  $s_{5,1} = \hat{d}_{6,4} \oplus \hat{d}_{7,2} \oplus \hat{d}_{7,3} \oplus \hat{d}_{8,1} \oplus \hat{d}_{8,2} \oplus \hat{d}_{8,3} \oplus \hat{d}_{10,1}$  $s_{6,0} = \hat{d}_{1,3} \oplus \hat{d}_{2,2} \oplus \hat{d}_{2,3} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,4} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,2} \oplus \hat{d}_{4,4} \oplus \hat{d}_{5,1} \oplus \hat{d}_{5,2}$  $s_{6,1} = \hat{d}_{6,1} \oplus \hat{d}_{7,1} \oplus \hat{d}_{7,3} \oplus \hat{d}_{7,4} \oplus \hat{d}_{8,1} \oplus \hat{d}_{8,2} \oplus \hat{d}_{8,3} \oplus \hat{d}_{8,4} \oplus \hat{d}_{10,2}$  $s_{7,0} = \hat{d}_{1,1} \oplus \hat{d}_{1,4} \oplus \hat{d}_{2,1} \oplus \hat{d}_{2,3} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,2} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,2} \oplus \hat{d}_{4,3}$  $s_{7,1} = \hat{d}_{5,2} \oplus \hat{d}_{5,3} \oplus \hat{d}_{6,2} \oplus \hat{d}_{7,2} \oplus \hat{d}_{7,4} \oplus \hat{d}_{8,2} \oplus \hat{d}_{8,3} \oplus \hat{d}_{8,4} \oplus \hat{d}_{10,3}$  $s_{8.0} = \hat{d}_{1.1} \oplus \hat{d}_{2.1} \oplus \hat{d}_{2.4} \oplus \hat{d}_{3.2} \oplus \hat{d}_{4.2} \oplus \hat{d}_{4.4} \oplus \hat{d}_{5.3} \oplus \hat{d}_{6.3}$  $s_{8,1} = \hat{d}_{6,4} \oplus \hat{d}_{7,1} \oplus \hat{d}_{7,2} \oplus \hat{d}_{8,1} \oplus \hat{d}_{8,2} \oplus \hat{d}_{8,4} \oplus \hat{d}_{10,4}$  $s_{9,0} = \hat{d}_{1,3} \oplus \hat{d}_{2,1} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,2} \oplus \hat{d}_{4,2} \oplus \hat{d}_{5,1} \oplus \hat{d}_{5,3} \oplus \hat{d}_{5,4}$  $s_{9,1} = \hat{d}_{6,3} \oplus \hat{d}_{6,4} \oplus \hat{d}_{7,1} \oplus \hat{d}_{7,2} \oplus \hat{d}_{7,3} \oplus \hat{d}_{8,2} \oplus \hat{d}_{8,3} \oplus \hat{d}_{11,1}$

PATENTED OCT 16 1973

3,766,521

# SHEET 36 OF 39

|   | $s_{10,0} = \hat{d}_{1,1} \oplus \hat{d}_{1,4} \oplus \hat{d}_{2,1} \oplus \hat{d}_{2,2} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,2} \oplus \hat{d}_{3,3} \oplus \hat{d}_{4,3} \oplus \hat{d}_{5,2} \oplus \hat{d}_{5,4}$                                                                                                                |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | $s_{10,1} = d_{6,4} \oplus d_{7,1} \oplus d_{7,2} \oplus d_{7,3} \oplus d_{7,4} \oplus d_{8,1} \oplus d_{8,3} \oplus d_{8,4} \oplus d_{11,2}$                                                                                                                                                                                          |  |

|   | $s_{11,0} = \hat{d}_{1,1} \oplus \hat{d}_{1,2} \oplus \hat{d}_{2,1} \oplus \hat{d}_{2,2} \oplus \hat{d}_{2,3} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,3} \oplus \hat{d}_{3,4} \oplus \hat{d}_{4,4} \oplus \hat{d}_{4,4}$                                                                                                                |  |

|   | $s_{11,1} = \hat{d}_{5,1} \oplus \hat{d}_{5,3} \oplus \hat{d}_{6,1} \oplus \hat{d}_{7,1} \oplus \hat{d}_{7,2} \oplus \hat{d}_{7,4} \oplus \hat{d}_{8,2} \oplus \hat{d}_{8,4} \oplus \hat{d}_{11,3}$                                                                                                                                    |  |

|   | $s_{12,0} = \hat{d}_{1,2} \oplus \hat{d}_{2,2} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,4} \oplus \hat{d}_{4,1} \oplus \hat{d}_{5,2} \oplus \hat{d}_{5,3} \oplus \hat{d}_{6,2}$                                                                                                                                     |  |

|   | $s_{12,1} = \overset{\land}{d}_{6,3} \oplus \overset{\land}{d}_{6,4} \oplus \overset{\land}{d}_{7,1} \oplus \overset{\land}{d}_{7,2} \oplus \overset{\land}{d}_{7,4} \oplus \overset{\land}{d}_{8,1} \oplus \overset{\land}{d}_{8,2} \oplus \overset{\land}{d}_{11,4}$                                                                 |  |

|   | $s_{13,0} = \hat{d}_{1,1} \oplus \hat{d}_{1,4} \oplus \hat{d}_{2,2} \oplus \hat{d}_{2,3} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,3} \oplus \hat{d}_{3,4} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,2}$                                                                                                                |  |

|   | $s_{13,1} = \overset{\land}{d}_{4,4} \oplus \overset{\land}{d}_{5,1} \oplus \overset{\land}{d}_{5,2} \oplus \overset{\land}{d}_{5,4} \oplus \overset{\land}{d}_{6,2} \oplus \overset{\land}{d}_{6,3} \oplus \overset{\land}{d}_{6,4} \oplus \overset{\land}{d}_{7,1} \oplus \overset{\land}{d}_{8,1} \oplus \overset{\land}{d}_{12,1}$ |  |

| · | $s_{14,0} = \hat{d}_{1,1} \oplus \hat{d}_{1,2} \oplus \hat{d}_{2,3} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,2} \oplus \hat{d}_{3,4} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,2} \oplus \hat{d}_{4,3}$                                                                                                                                     |  |

|   | $s_{14,1} = \hat{d}_{5,1} \oplus \hat{d}_{5,2} \oplus \hat{d}_{5,3} \oplus \hat{d}_{6,3} \oplus \hat{d}_{6,4} \oplus \hat{d}_{7,2} \oplus \hat{d}_{8,2} \oplus \hat{d}_{12,2}$                                                                                                                                                         |  |

|   | $s_{15,0} = \hat{d}_{1,2} \oplus \hat{d}_{1,3} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,1} \oplus \hat{d}_{3,3} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,2} \oplus \hat{d}_{4,3} \oplus \hat{d}_{4,4}$                                                                                                                                     |  |

|   | $s_{15,1} = \hat{d}_{5,1} \oplus \hat{d}_{5,2} \oplus \hat{d}_{5,3} \oplus \hat{d}_{5,4} \oplus \hat{d}_{6,4} \oplus \hat{d}_{7,3} \oplus \hat{d}_{8,3} \oplus \hat{d}_{12,3}$                                                                                                                                                         |  |

|   | $s_{16,0} = \hat{d}_{1,3} \oplus \hat{d}_{2,1} \oplus \hat{d}_{2,2} \oplus \hat{d}_{2,3} \oplus \hat{d}_{2,4} \oplus \hat{d}_{3,2} \oplus \hat{d}_{3,3} \oplus \hat{d}_{4,1} \oplus \hat{d}_{4,3}$                                                                                                                                     |  |

|   | $s_{16,1} = \hat{d}_{5,1} \oplus \hat{d}_{5,3} \oplus \hat{d}_{6,1} \oplus \hat{d}_{6,2} \oplus \hat{d}_{6,3} \oplus \hat{d}_{6,4} \oplus \hat{d}_{7,4} \oplus \hat{d}_{8,4} \oplus \hat{d}_{12,4}$                                                                                                                                    |  |

|   |                                                                                                                                                                                                                                                                                                                                        |  |

# FIG. 7B

### PATENTED OCT 1 6 1973

3,766,521

### SHEET 37 OF 39

# PATENTED OCT 1 6 1973

3,766,521

### SHEET 38 OF 39

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\hat{d}_{5,1} = d_{5,1} \oplus (G_{5,6} \wedge e_{5,1})$                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\hat{d}_{5,2} = d_{5,2} \oplus (G_{5,6} \wedge e_{5,2})$                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\hat{d}_{5,3} = d_{5,3} \oplus (G_{5,6} \wedge e_{5,3})$                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\hat{d}_{5,4} = d_{5,4} \oplus (G_{5,6} \wedge e_{5,4})$                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\hat{d}_{6,1} = d_{6,1} \oplus (G_{5,6} \wedge e_{6,1})$                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | â6,2 = d6,2 ⊕ (G5,6 ∧ e6,2)                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\hat{d}_{6,3} = d_{6,3} \oplus (G_{5,6} \wedge e_{6,3})$                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6,4 = d 6,4 ⊕ ( G 5,6 ∧ e 6,4)                                               |  |

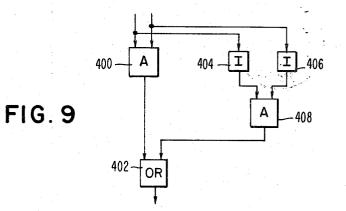

| FIG.8B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\hat{d}_{7,1} = d_{7,1} \oplus (G_{7,8} \wedge e_{7,1})$                    |  |